![PDF] Design of a Low-Power High-Speed T-Flip- Flop Using the Gate-Diffusion Input Technique | Semantic Scholar PDF] Design of a Low-Power High-Speed T-Flip- Flop Using the Gate-Diffusion Input Technique | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/546bbc334a9636e1c4ea48cebac0f25ed122729d/2-Figure4-1.png)

PDF] Design of a Low-Power High-Speed T-Flip- Flop Using the Gate-Diffusion Input Technique | Semantic Scholar

Novel ultra-energy-efficient reversible designs of sequential logic quantum-dot cellular automata flip-flop circuits | The Journal of Supercomputing

Test circuit schematic for three-TAG flip-flops. Each d-type flip-flop... | Download Scientific Diagram

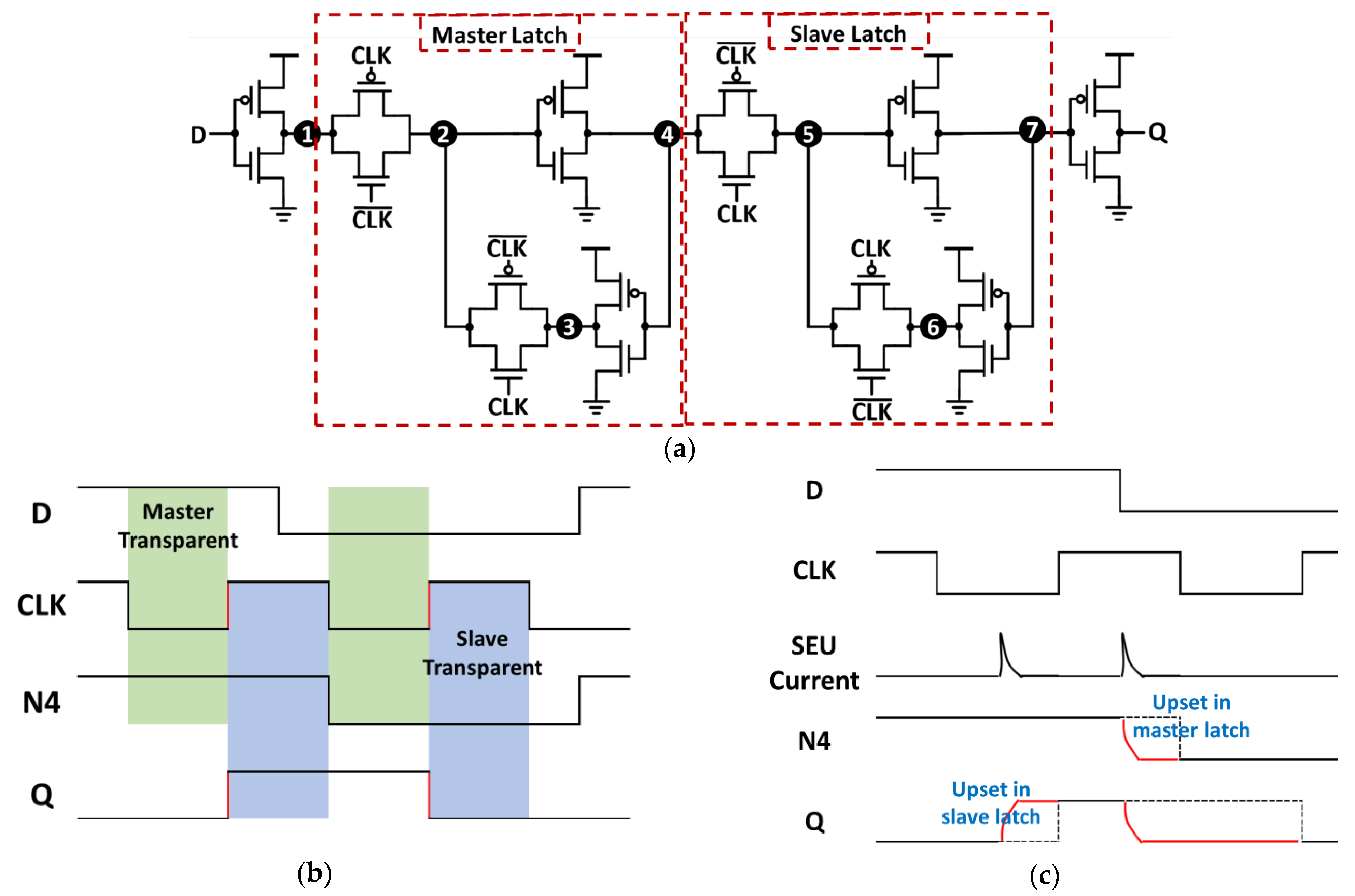

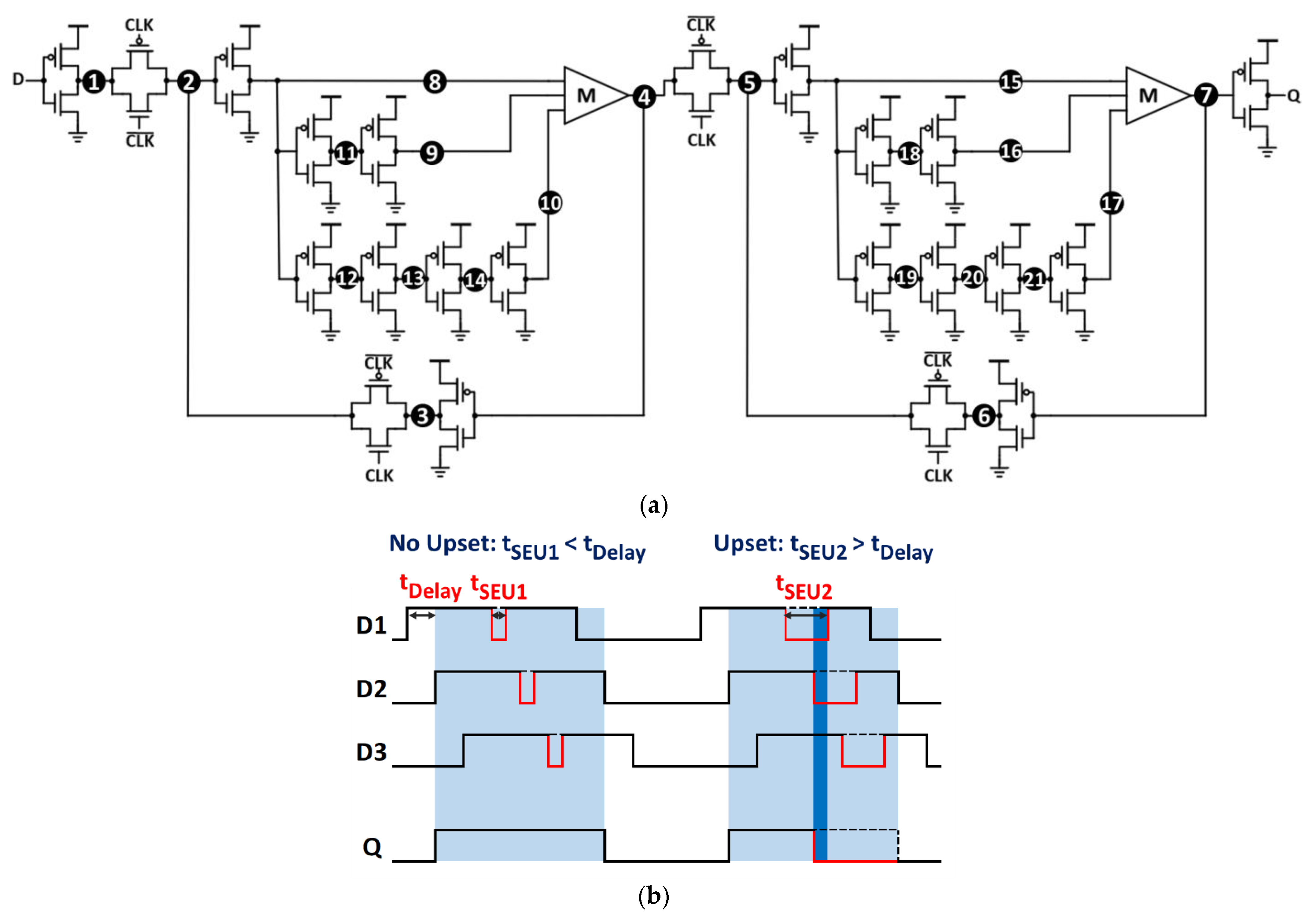

Electronics | Free Full-Text | Categorization and SEU Fault Simulations of Radiation-Hardened-by-Design Flip-Flops

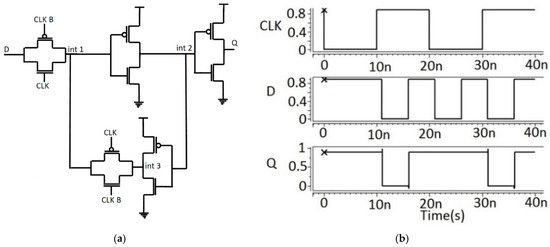

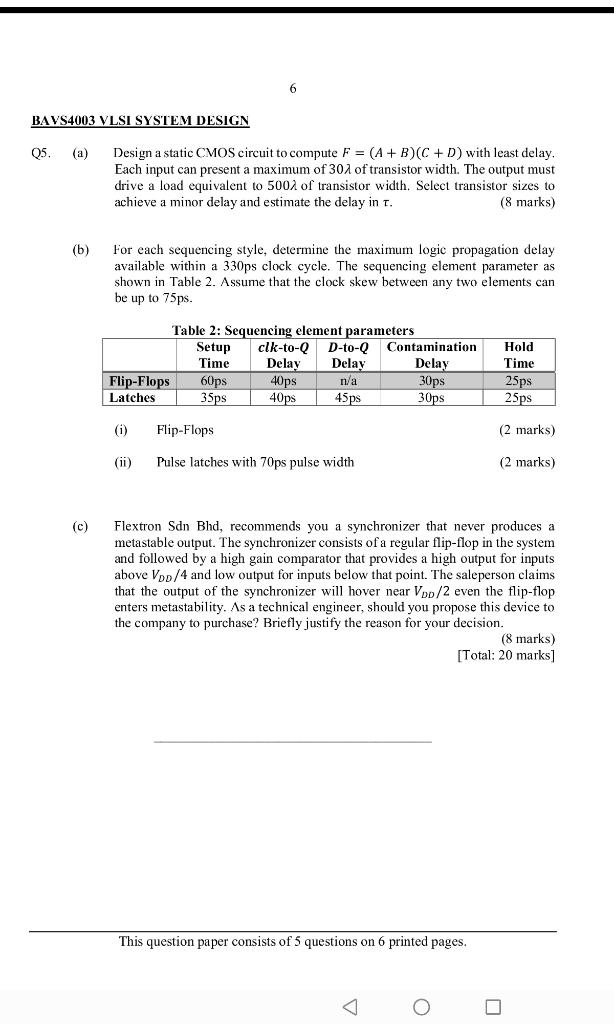

Electronics | Free Full-Text | Low-Cost Soft Error Robust Hardened D-Latch for CMOS Technology Circuit

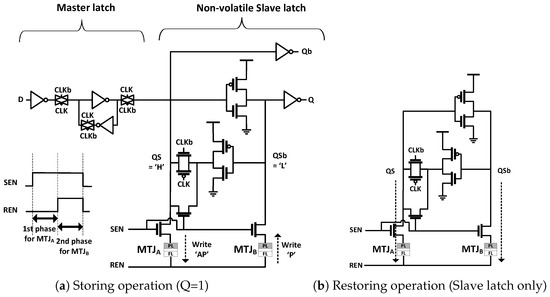

Micromachines | Free Full-Text | Fine-Grained Power Gating Using an MRAM- CMOS Non-Volatile Flip-Flop

Transmission Gate Flip-Flop (TGFF). Transmission Gate Flip-Flop (TGFF). | Download Scientific Diagram

Novel ultra-energy-efficient reversible designs of sequential logic quantum-dot cellular automata flip-flop circuits | The Journal of Supercomputing

![PDF] Differential static ultra low-voltage CMOS flip-flop for high speed applications | Semantic Scholar PDF] Differential static ultra low-voltage CMOS flip-flop for high speed applications | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/aba79f96f2b565b16da053c8c3795311997eedba/2-Figure1-1.png)

PDF] Differential static ultra low-voltage CMOS flip-flop for high speed applications | Semantic Scholar

Electronics | Free Full-Text | Categorization and SEU Fault Simulations of Radiation-Hardened-by-Design Flip-Flops

Figure2. (a)The Design of CMOS DET flip-flop (b) A Modified design of... | Download Scientific Diagram

![Activity: CMOS Logic Circuits, D Type Latch [Analog Devices Wiki] Activity: CMOS Logic Circuits, D Type Latch [Analog Devices Wiki]](https://wiki.analog.com/_media/university/courses/alm1k/cd4007_pinout.png?w=400&tok=cdb082)